- 您现在的位置:买卖IC网 > Sheet目录3882 > PIC24F08KL301-I/SS (Microchip Technology)IC MCU 16BIT 8KB FLASH 20-SSOP

CHAPTER 6 CLOCK GENERATION FUNCTION

User’s Manual U15905EJ2V1UD

207

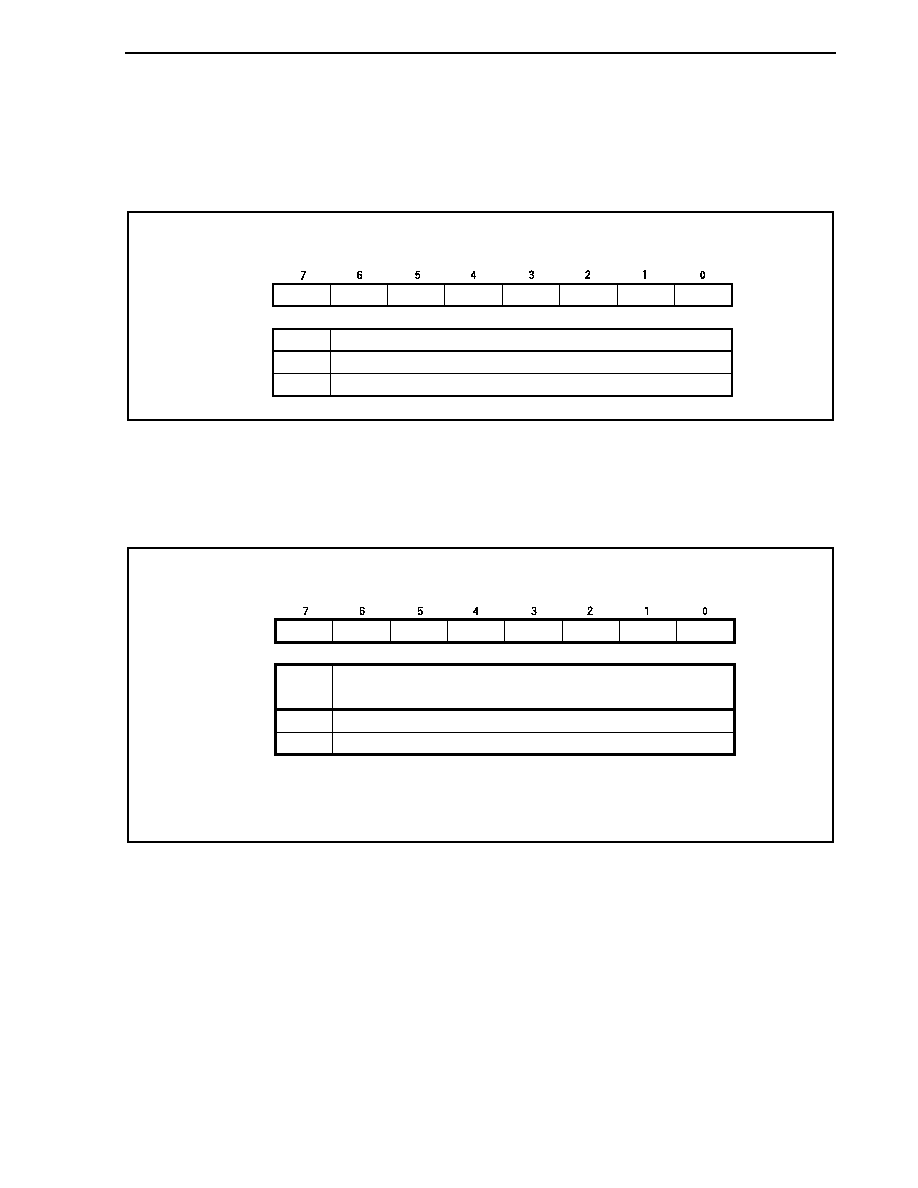

(2) Power save control register (PSC)

The power save control register (PSC) is a special register.

Data can be written to this register only in

combination of specific sequences (refer to 3.4.8 Special registers).

This register can be read or written in 8-bit or 1-bit units.

This register is cleared to 00H after reset.

0

PSC

0

STP

0

Normal mode

IDLE/software STOP mode

STP

0

1

Setting of IDLE/software STOP mode

After reset: 00H

R/W

Address: FFFFF1FEH

< >

(3) Power save mode register (PSMR)

This is an 8-bit register that controls the operation status and clock operation in the power save mode.

It can be read or written in 8-bit or 1-bit units.

This register is cleared to 00H after reset.

0

IDLE mode

Software STOP mode

PSM

0

1

Specifies operation in software standby mode

(valid when bit 1 (STP) of the PSC register is set to 1)

PSMR

0

PSM

After reset: 00H

R/W

Address: FFFFF820H

< >

Cautions 1. Be sure to clear bits 1 to 7 of the PSMR register to 0.

2. The PSM bit is valid only when the STP bit of the PSC register is set to 1.

(4) Oscillation stabilization time selection register (OSTS)

This is an 8-bit register that controls the operation status and clock in the power save mode.

Refer to 10.3 (1) Oscillation stabilization time selection register (OSTS).

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF1220T-I/ML

IC MCU FLASH 2KX16 EEPROM 28QFN

PIC18LF1220T-I/SO

IC MCU FLASH 2KX16 EEPROM 18SOIC

PIC16F716-I/SS

IC PIC MCU FLASH 2KX14 20SSOP

PIC18F1320T-E/ML

IC MCU FLASH 4KX16 EEPROM 28QFN

PIC16LF87T-I/ML

IC MCU FLASH 4KX14 EEPROM 28QFN

PIC18F25J10-I/SS

IC PIC MCU FLASH 16KX16 28SSOP

PIC16F88T-E/SS

IC MCU FLASH 4KX14 EEPROM 20SSOP

PIC16C621A-04/SO

IC MCU OTP 1KX14 COMP 18SOIC

相关代理商/技术参数

PIC24F08KL301T-I/MQ

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL301T-I/SO

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL301T-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Low-Power, Low-Cost, General Purpose 16-Bit Flash Microcontrollers with nanoWatt XLP Technology

PIC24F08KL302-I/ML

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/MQ

功能描述:16位微控制器 - MCU 8KB FL 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/SO

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/SP

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT